M31 LPDDR4X multi-PHY supports both LPDDR4 and LPDDR4X memory interfaces at speed up to 4267Mbps, making it an ideal solution for ASICS, ASSPs, SOC and POP that require high performance memory interfaces. The multi-interface PHY can be used in a variety of applications, including automotive (autonomous driving), mobile (smart phones) and enterprise (laptops and desktops).

- IP Product Lists

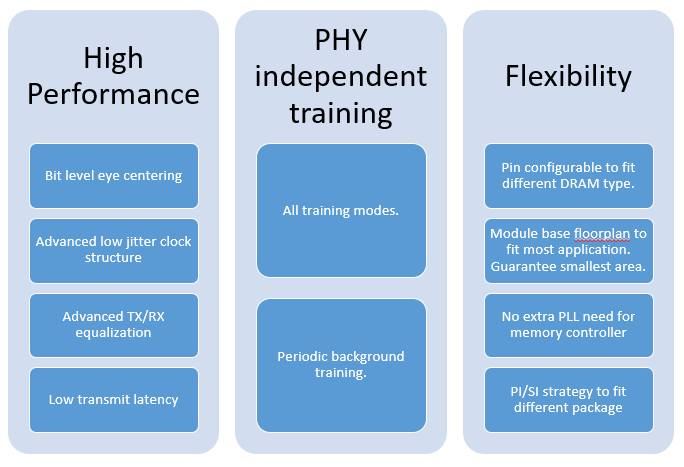

- Features

- Multi-interface support: LPDDR4 up to 4267Mbps, LPDDR4X up to 4267Mpbs

- Supports LPDDR4X 0.6V VDDQ

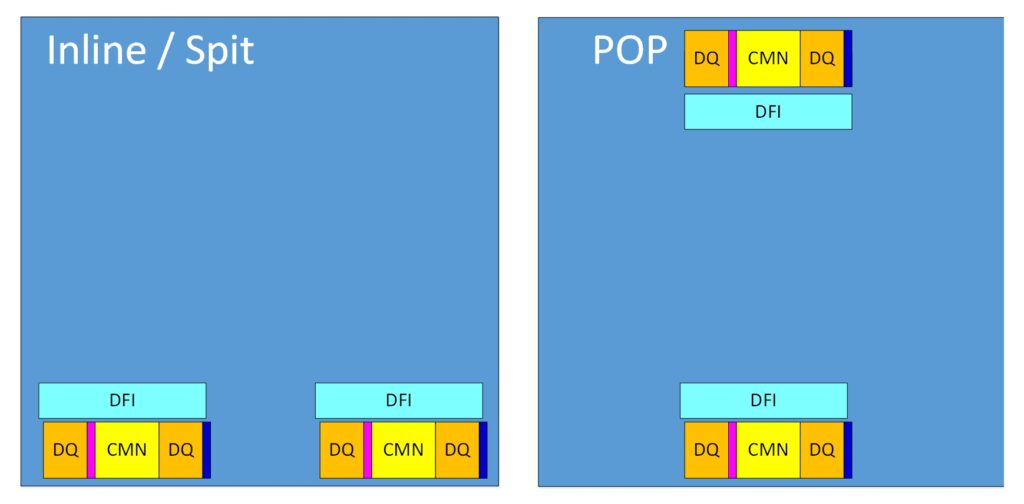

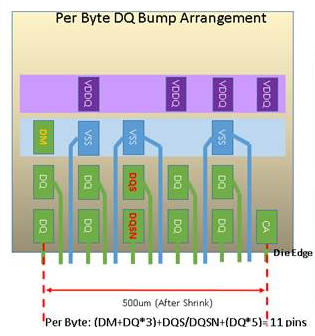

- Optimized for high performance and integration flexibility. The harden IP included 8-bit data blocks, 6-bit C/A blocks, clock blocks, PLL and DLL. IP pin-out can be configured to optimize for LPDDR4/4X.

- High resolution read/write timing control

- Per bit deskew on read/write data path

- Multiple PHY independent training mode, including periodic background training

- Low power mode

- Dynamic frequency scaling

- Testability support: Scan, ATPG with OPCG, BIST with loopback test

- Advanced equalization, including TX FFE and RX DFE

- PI/SI design guidelines to ensure high data rate performance

- Advance clock structure to minimize jitter and automated interface timing margins