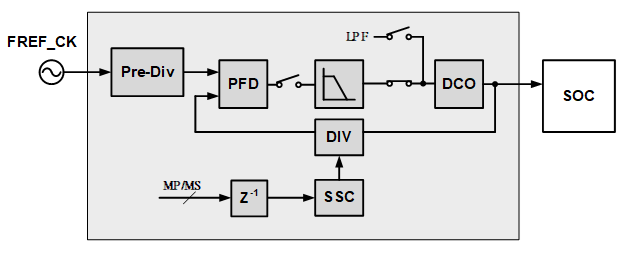

M31 Digital-PLL is a core-power only programmable phase-locked loop (PLL) for frequency synthesis. It supports multiple modes of operation for several application conditions, such as Phase-locked loop (PLL) /Fractional-N phase-locked loop (FNPLL) /Spread spectrum clocking (SSC)/ Oscillator (OSC). M31 Digital-PLL has excellent immunity to power supply noise, making it ideally suited for use in noisy ASIC/SoC environments and is available as a single macro for easy integration into any ASIC/SoC.

- IP Product Lists

- Features

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

- Supports 24-bit fractional accuracy

- Supports down spread-spectrum clocking (SSC) technology

- Supports retention OSC operation

- Embedded lock-detect flag

- Embedded scan chain for mass production

- Full deliverables to ease ASIC/SoC integration