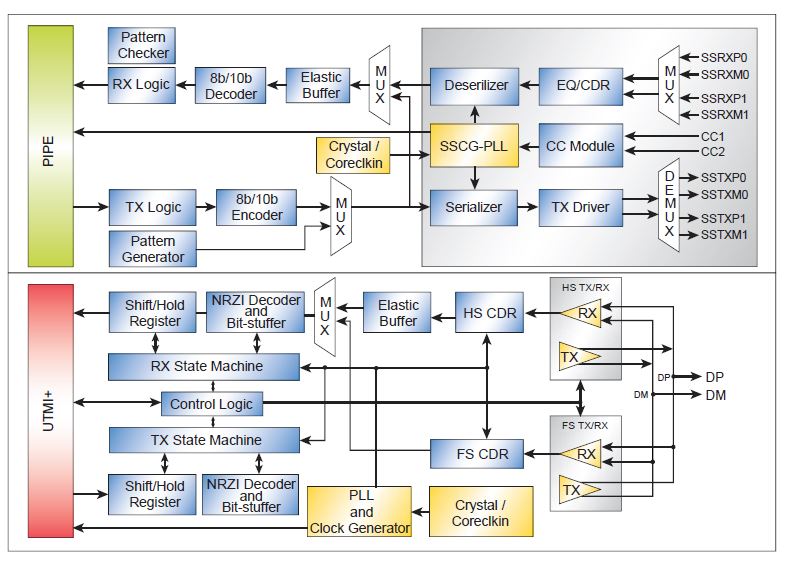

M31 USB 3.2 Gen2 (support x1/x2) transceiver IP provides a complete range of USB 3.2 Gen2 host and peripheral applications up to 10x2Gbps. It is compliant with the PIPE4.0 and UTMI+ specifications. The USB 3.2 Gen2 IP integrates high-speed mixed signal circuits to support Gen2 and Gen1 traffic and is backward compatible with 480Mbps high-speed, 12Mbps full-speed, and 1.5Mbps low-speed data rates. To support USB Type-C connectors, the USB 3.2 Gen2 IP also integrates the active switch to support the bi-directional plug-in and the specific functions (USB attachment cable orientation detection and VBUS configuration) through the CC1/CC2 pins defined in Type-C connector.

- IP Product Lists

- USB 3.2 Gen2 Features

- USB 3.2 Gen1 Features

- Worldwide smallest USB 3.2 Gen2 PHY IP (e.g. IP size @28HPC+ is smaller than 0.7mm²)

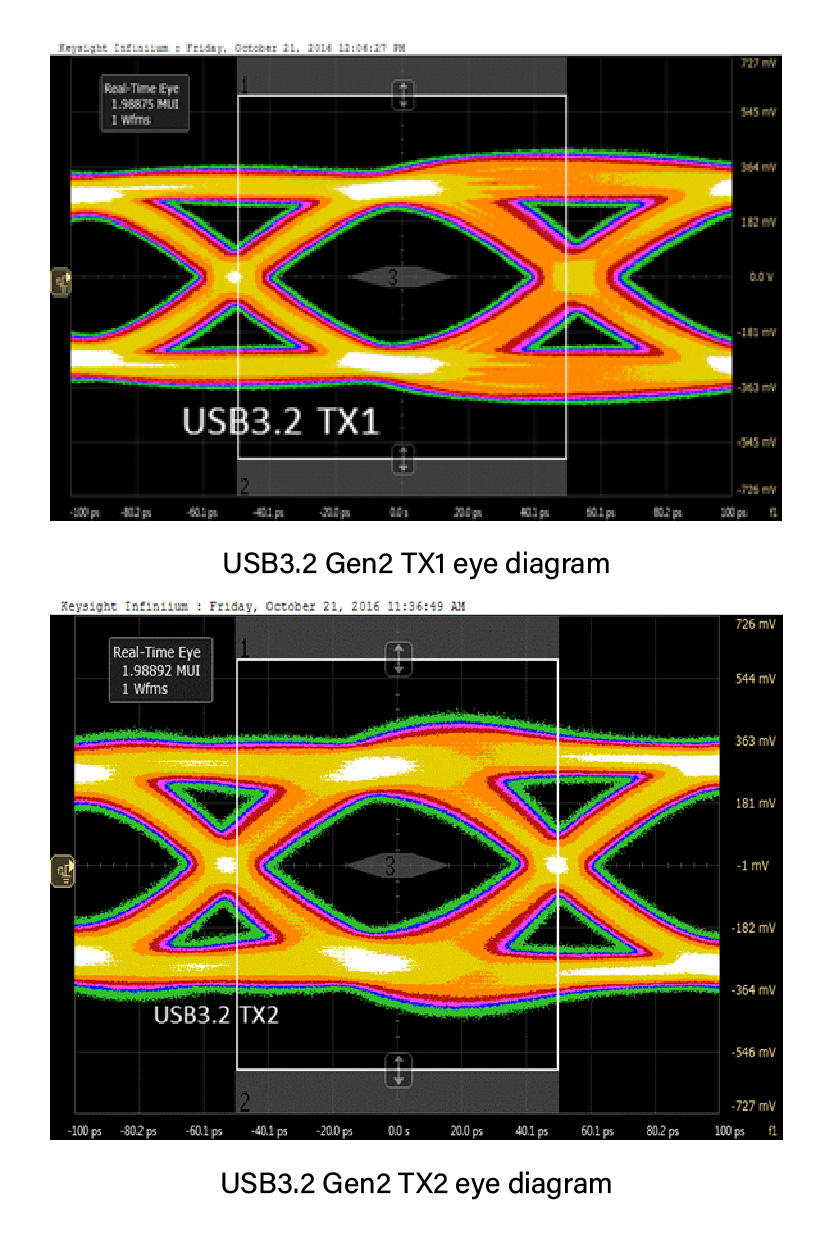

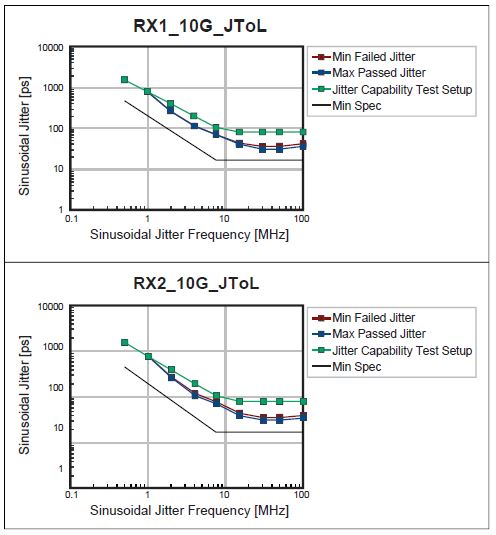

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2 and 2.0 electrical specifications

- Supports clock inputs from 10/12/19.2/24/25/27/30/40MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

- Integrates an active switch to support the orientation-less connection with USB Type-C connectors

- Provides an auxiliary CC module IP to support USB Type-C related functions

- Supports both Wire-bond and flip-chip package types

- Supports internal loop back and BIST functions for mass production testing

- Worldwide smallest USB 3.2 Gen1x1 PHY IP (e.g. IP size @28HPC+ is smaller than 0.5mm²)

- Fully compliant with Universal Serial Bus USB 3.2 Gen1x1 and 2.0 electrical specifications

- Compliant with PIPE4.0 and UTMI+ specification (Super-Speed, High-Speed, Full-Speed and Low-Speed functions)

- Supports clock inputs from 25MHz crystal oscillator or external 25MHz clock source

- Provides plenty of register controls for TX, RX, SSCG-PLL and CDR electrical parameters

- Silicon proven and mass production IP records