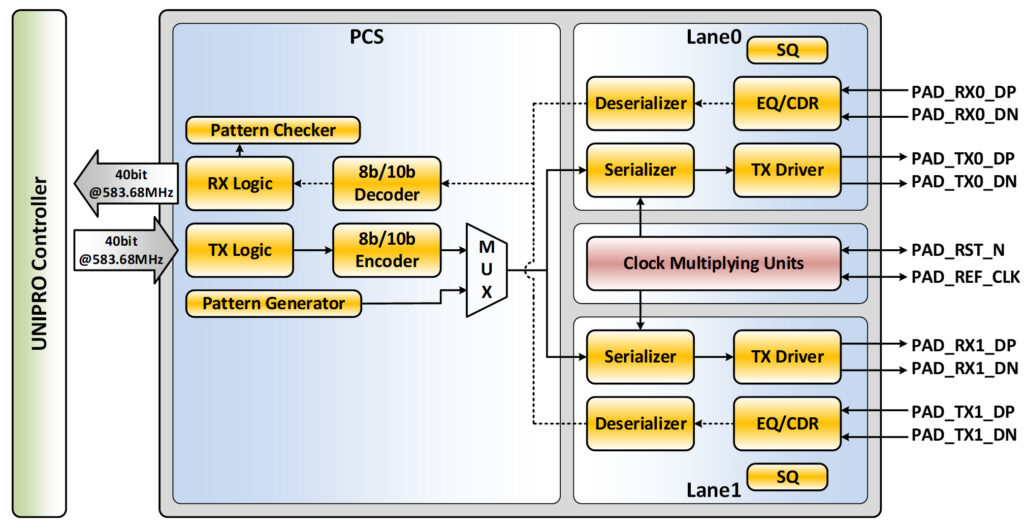

MIPI M-PHY v5.0

MIPI M-PHY is a serial interface technology with high bandwidth capabilities, which is particularly developed for mobile applications to obtain low pin counts along with excellent power efficiency. As a MIPI Alliance contributor and leading Interface IP provider, M31 provides silicon-proven and low-power M-PHY in various process nodes. The M-PHY IP is optimized for UFS (Universal Flash Storage) applications, follows MIPI M-PHY v5.0 spec, supports a wide range of high-speed (HS) and low-speed (LS) data transfer, and complies with the RMMI interface for seamless integration with upside controllers. Moreover, M31 also provides various lane configurations for the M-PHY IP to meet different bandwidth requirements.

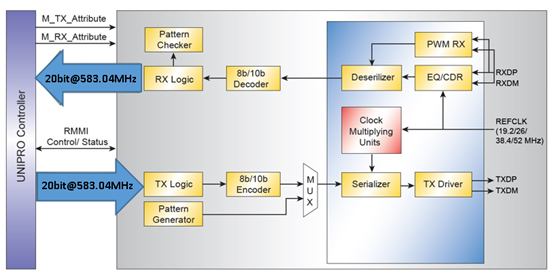

MIPI M-PHY v4.1/v3.1

MIPI M-PHY is a serial interface technology with high bandwidth capabilities, which is particularly developed for mobile applications to obtain low pin counts along with excellent power efficiency. As a MIPI Alliance contributor and leading Interface IP provider, M31 provides silicon-proven and low-power M-PHY in various process nodes. The M-PHY IP is optimized for UFS (Universal Flash Storage) applications, follows MIPI M-PHY v4.1 spec, supports a wide range of high-speed (HS) and low-speed (LS) data transfer, and complies with the RMMI interface for seamless integration with upside controllers. Moreover, M31 also provides various lane configurations for the M-PHY IP to meet different bandwidth requirements.

- IP Product Lists

- M-PHY v5.0 Features

- M-PHY v4.1 Features

- M-PHY v3.1 Features

- Complies with MIPI M-PHY specification v5.0 and CTS v5.0

- Support M-PHY RMMI spec. (40/80bits) for UFS host & device applications

- Support 2Tx/2Rx structure with 1-port device only

- Optimized for High-Speed gear G1A/G1B/G2A/G2B/G3A/G3B/G4A/G4B/G5A/G5B

- Support Type-1 PWM G1 NT in LS PWM mode

- Support multiple signal amplitude

- Build-in at-speed DFT and BIST functions

- Adaptive EQ for MPHY HSG5

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2)

- High speed gears, HS-G1A/B, HS-G2A/B, HS-G3A/B and HS-G4A/B with scalable power consumptions

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

- Supports reference-less function during low-speed operation

- Common lane configuration facilitates the lane scalability

- Low latencies to switch to/from different power states

- Supports multiple signal amplitudes

- Supports internal loopback BIST functions for at-speed mass production testing

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

- Supports reference-less function during low-speed operation

- Common lane configuration facilitates the lane scalability

- Low latencies to switch to/from different power states

- Supports multiple signal amplitudes

- Supports internal loopback BIST functions for at-speed mass production testing

- Certified with ASIL-B of ISO 26262